光刻机一直是半导体领域的一个热门话题。

从早期的深紫外光刻机(DUV)起步,其稳定可靠的性能为半导体产业的发展奠定了坚实基础;再到后来的极紫外光刻机(EUV)以其独特的极紫外光源和更短的波长,成功将光刻精度推向了新的高度;再到如今的高数值孔径光刻机(High-NA)正式登上历史舞台,进一步提升了光刻的精度和效率,为制造更小、更精密的芯片提供了可能。

ASML官网显示,其组装了两个TWINSCAN EXE:5000高数值孔径光刻系统。其中一个由ASM与imec合作开发,将于2024年安装在ASML与imec的联合实验室中,预计2025年投入量产。另一个由英特尔在2018年订购, 2023 年 12 月,ASML正式向英特尔交付了首个High-NA EUV 光刻系统——TWINSCAN EXE:5000的首批模块。

01

首台High-NA EUV光刻机拆箱

今年1月,ASML首台High-NA EUV光刻机的主要组件抵达英特尔,随后在3月初,英特尔分享了一段视频,展示了在英特尔位于美国俄勒冈州的 D1X 工厂内,ASML 工程团队安装调试的部分画面。

ASML 发言人 Monique Mols 在公司举行的媒体参观活动中表示,安装这台重达 150000 公斤的系统共计用时 6 个月,需要 250 个集装箱和 250 名工程师。一旦组装完成,这台机器将高达3层楼高,这迫使英特尔建造一个新的(更高的)厂房扩建来容纳它。据估计,每台这样的High-NA EUV光刻机的价格可能在3亿至4亿美元之间。

值得注意的是,英特尔也是业界首个订购 TWINSCAN EXE:5200光刻机的公司,该订单的下单时间在2022年1月。

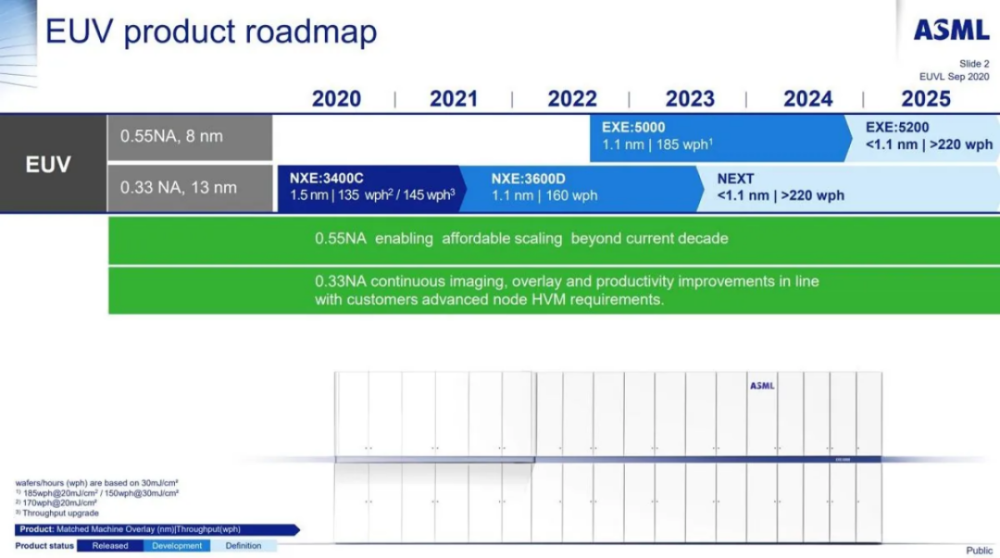

根据ASML的路线图,第一代的High-NA EUV光刻机TWINSCAN EXE:5000或许主要是被晶圆制造商用于相关实验与测试,以便公司更好地了解High-NA EUV设备的使用,获得宝贵经验。实际量产将会依赖于2024年底出货的TWINSCAN EXE:5200。

02

为什么需要High-NA光刻机?

DUV向EUV迈进

在DUV世代,科学家们一直进行研究将DUV光刻技术 推向极限。为了减小可光刻的最小特征的尺寸(称为临界尺寸 (CD)),可以通过调整两个主要的参数:光的波长 λ 和数值孔径 NA。

光刻分辨率(R)主要由三个因数决定,分别是光的波长(λ)、光可穿过透镜的最大角度(镜头孔径角半角θ)的正弦值(sinθ)、折射率(n)以及系数k1有关。除了光刻分辨率之外,焦距深度( Depth of Focus,DOF)也至关重要,大的焦深可以增大刻蚀的清晰范围,提高光刻的质量,而焦距深度也可以通过提高系统的折射率(n)来改进。

然而,现在的 DUV 系统中已经没有多少空间可以调整这些参数了。

进入EUV世代,EUV 光刻则能够对波长参数进行重大调整:它使用 13.5 nm 光,而最高分辨率 DUV 系统则使用 193 nm 光。第一个预生产 EUV 光刻平台 NXE 于 2010 年首次发货时,它的 CD 从 DUV 的 30 nm 以上下降到 EUV 的 13 nm。

此外,EUV光刻机不仅调整了波长参数,还具备光源系统、光学镜头、双工作台系统等核心技术,这些技术的结合使得EUV光刻机能够实现高效的投影光刻,无损伤地处理任意图形。

EUV向High-NA EUV迈进

ASML目前的EUV工具的数值孔径为0.33,可实现13.5nm左右的分辨率,透过单次曝光,可以产生26nm的最小金属间距和25-30nm尖端到尖端的近似互连空间间距,这些尺寸足以满足4/5nm节点制程的生产需求。尽管如此,业界仍然需要更小的21-24nm间距的3nm制程工艺,这就是为什么台积电的N3B制程技术被设计为使用标准EUV双图案化技术来实现更小的间距,但这种方法将会相当昂贵。

改变波长之后再进一步提升EUV光刻机的分辨率就要从NA指标上下手了。

在这里解释一下“NA”即光学系统的数值孔径,表示光线的入射角度,使用更大的NA透镜可以打印出更小的结构,目前的EUV光刻机使用的还是NA=0.33的物镜系统,下一代的目标就是NA=0.5及以上的光学系统。

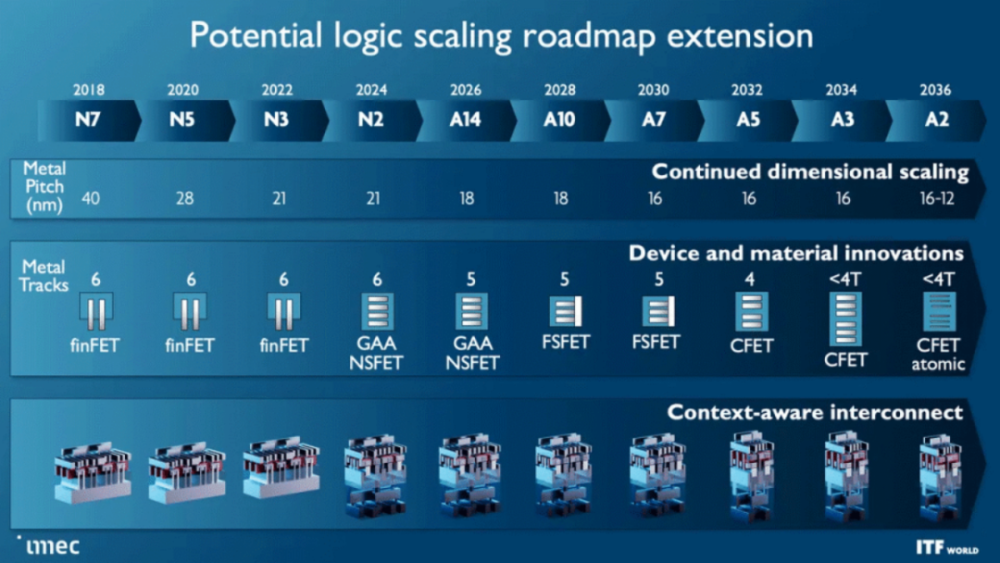

因此,High-NA应运而生。目前ASML已经开始交付的首款High-NA EUV系统数值孔径已经由传统EUV的0.33提升到了0.55,分辨率也由13.5nm提升到了8nm,可以实现16nm的最小金属间距,对于2nm以下制程节点将非常有用。根据Imec的预计,这即使对于1nm节点技术,High-NA EUV系统也能提供解决方案。另外,在生产效率方面,High-NA EUV系统每小时可光刻超过 185 个晶圆,与已在大批量制造中使用的 EUV 系统相比还有所增加。ASML还制定了到 2025 年将新一代High-NA EUV系统(EXE:5200)的生产效率提高到每小时 220 片晶圆的路线图。

03

High-NA EUV光刻机对英特尔来说意味什么?

High-NA EUV被认为是可以降低工艺复杂性和制造成本,并是制造2nm及以下的尖端制程的关键设备。High-NA 不仅需要新的光学器件,还需要新的光源材料,例如德国蔡司在真空中制造的一个由抛光、超光滑曲面镜组成的光学系统,甚至还需要新的更大的厂房来容纳这种机器,这都将需要大量投资。

即便如此,为了保持半导体的性能、功率、面积和成本(PPAc)等方面的优势,已经领先的制造商们诸如台积电、三星、英特尔、SK海力士等世界头部逻辑芯片和存储芯片制造商,为了率先并更多拿到ASML最先进的光刻机已经争得不可开交。早在 2020 ~ 2021 年,ASML 就表示已经收到了三家客户的 High-NA 意向订单,共提供多达 12 套系统。

英特尔率先拿到该设备,无疑会极大地提升其芯片制造能力和效率,并帮助英特尔在未来先进制程技术的竞争中取得先行优势。通过使用这种先进的光刻技术,英特尔可以生产出2nm及更小、更快的芯片,从而在市场上获得更大的竞争优势。此外,随着芯片制程的缩小,英特尔可以进一步降低生产成本,提高产品竞争力。

此外,在高数值孔径学习方面,英特尔将领先于其竞争对手,这将为其带来多项优势。具体来说,由于英特尔很可能是第一家使用高数值孔径工具启动大批量生产的公司,因此晶圆厂工具生态系统将不可避免地遵循其要求。上述要求可能会转化为行业标准,这可能会使英特尔比台积电和三星更具优势。

目前英特尔已经完成了英特尔 18A(1.8nm)和英特尔 20A(2nm)制造工艺的开发,其中英特尔 20A计划于2024年上半年投入使用,而进展良好的英特尔 18A制造技术也将提前到2024年下半年进入大批量制造。这表明英特尔对High-NA EUV技术的应用充满信心,并计划在未来几年内将这一技术应用于其主要的芯片生产中。High-NA EUV光刻技术,可以给英特尔带来更低的生产成本和更高的产品竞争力。

综上所述,英特尔获得的全球首台High-NA EUV光刻机不仅标志着该公司在半导体制造领域的一大进步,也展示出其在推动先进光刻技术发展方面的决心和能力。

04

ASML的High-NA EUV光刻机产量

目前ASML已从英特尔和SK海力士等公司获得了High-NA EUV光刻机的订单,数量在10至20台之间。与此同时,ASML计划到2028年,每年生产20台High-NA EUV光刻机,以满足市场的需求。

根据集邦咨询的报告显示,ASML将在2024年生产最多10台新一代High-NA EUV极紫外光刻机,其中英特尔就定了多达6台。

三星也在积极寻求获得High-NA EUV。2022年 6 月三星电子与ASML就采购高数值孔径EUV达成协议。今年2月,三星电子与荷兰设备巨头ASML再次宣布,将在韩国共同投资设立半导体先进制程研发中心,并计划自2027年起引入High-NA EUV设备。

三星此次与ASML的合作表明了其在半导体技术领域的雄心壮志。通过共同研发和引进High-NA EUV设备,三星将能够进一步提升其芯片制造工艺,并在全球半导体市场中获得更大的竞争优势。值得注意的是,High-NA EUV设备的引进和应用也面临着挑战,包括设备价格高昂、良率问题以及生产过程中的技术难题等。

三星负责存储器生产的研究员Young Seog Kang曾表示:用户最关心的是总成本问题,前Low-NA已经投入使用,相比High-NA EUV,芯片制造商可能更愿意使用更经济可行的Low-NA EUV以双重曝光或采用先进封装技术作为补充。因此High-NA EUV可能更有利于逻辑芯片制造,存储器或面临成本问题。

相比之下,台积电并不急于在短期内采用高数值孔径 EUV,华兴资本董事总经理吴思浩说,台积电可能需要数年时间才能在 2030 年或以后赶上这一潮流。

SemiAnalysis 和华兴资本分析师指出,台积电暂时不会跟进采用这项技术,主因在于,使用高数值孔径 EUV 的成本,可能比使用 Low-NA EUV 还高,至少在初期是这样,尽管低成本的代价是生产出来的晶体管密度较低。台积电采用EUV的时间就比三星要晚几个月,但是要比英特尔早几年。

05

Hyper-NA EUV是未来十年的重要改变

近日,AMSL在其2023年度报告当中还披露了其未来更为先进的Hyper-NA EUV技术的进展。

ASML 技术长Martin van den Brink 在ASML 2023 年年度报告中表示,NA 值高于0.7 的Hyper-NA 微影曝光设备无疑的是一个发展芯片生产技术的机会,而且从2030 年左右开始获得应用。预计,Hyper-NA 微影曝光设备可能与逻辑芯片最相关,并且将提供比High-NA 微影光设备更实惠的解决方案。而对ASML 来说,关键是Hyper-NA 正在推动整体EUV 发展平台,以改善成本和交货时间。

未来,随着制程工艺的继续推进,当进入1nm制程工艺节点之后,晶体管的金属间距将需要变得更小。届时晶圆制造商将需要比High-NA EUV光刻机更复杂的工具,这也是ASML为何计划开发出具有更高数值孔径Hyper NA EUV光刻机的原因。

凭借晶体管技术以及先进的制造工具的出现,2030年将进入7埃米(0.7nm)时代,2032年将有望进化到5埃米(0.5nm),2036年将有望实现2埃米(0.2nm)。

增加投影光学元件的数值孔径是一个成本高昂的决定,其中牵涉对微影曝光设备的设计需要进行重大改变。特别是这包括机器的物理尺寸、并需要开发许多新组件,还有成本增加的因素。ASML 最近透露,标准数值孔径EUV Twinscan NXE 售价约为1.83 亿美元,而High-NA EUV 的Twinscan EXE 的售价约为3.8 亿美元或更高。

至于,接下来的Hyper-NA 微影曝光设备的成本预计将会更高的情况下,ASML 必须解决两个问题,就是Hyper-NA 微影曝光设备是否可以在技术上实现,以及对于领先的逻辑芯片制造商来说是否在成本上负担得起。当前,全球只剩下三个领先的逻辑芯片制造商,包括英特尔、三星和台积电。日本的Rapidus 尚未发展成为有能力的竞争对手。因此,虽然需要Hyper-NA EUV 微影曝光设备,但它必须价格合理。

Martin van den Brink 曾经指出,Hyper-NA 微影曝光设备最终是否导入的决定,将取决于ASML能够降低成本的程度。然而,在ASML 与客户讨论了Hyper-NA EUV 微影曝光设备的必要性和可行性之后,客户使用Hyper-NA EUV 微影曝光设备来大规模生产逻辑和存储器芯片的技术条件已经存在,这预计将是下一个十年半导体产业的重要变化。

总结

半导体领域一直在热议的High-NA EUV光刻机一直是各国争相购买的目标。2022年,ASML将其组装的两个TWINSCAN EXE:5000高数值孔径光刻系统交付给了英特尔,开启了这个令人期待的新时代的开始。尽管在进入EUV世代后,EUV光刻能实现更高的分辨率和低的复杂度,但随着半导体厂商之间的竞争愈发激烈,High-NA EUV也将发挥关键作用。

Firstly, High-NA EUV光刻机可以减少临界尺寸和扫描范围的限制,为制造更小、更精密的芯片提供了可能性。正如EUV光刻实现了这个目标一样,High-NA EUV有望为用户降低生产工艺复杂性和制造成本,尤其是对于2nm以下的节点制程工艺。

Secondly, ASML的多套High-NA EUV光刻机正在推出,预计在2028年将达到最大产能。这意味着在未来几年内,ASML将引领整个半导体行业朝着更高密度、更精确的方向前进。并且,随着技术的进步,他们可能会在2030年左右引入Hyper-NA EUV技术。

However, it is worth noting that High-NA EUV光刻机面临的挑战也不容忽视。不仅仅是设备高昂的价格,还有良率问题和生产过程中的技术难题等。因此,虽然ASML将继续推出其更多的高精度组件,但解决这些问题仍需要时间和努力。

Overall, the introduction of High-NA EUV light刻机 represents a significant shift in the semiconductor industry. As MLU has already successfully delivered two high-nanometer EUV systems to Intel, this new era of EUV technology will open up possibilities for smaller and more precise chips. While challenges such as high costs and production processes remain, the development of this technology can provide significant cost savings and help companies in the future maintain competitiveness.