混合键合,这一备受期待的高级互联技术,似乎出现了新变故。

混合键合(Hybrid Bonding),主要用于在芯片的垂直堆叠中实现互连,在2.5D和3D封装领域颇受欢迎。它最大的特点是无凸块,结合了金属键合和非导电粘合剂(通常是氧化物或聚合物)的方法,能够在微观尺度上实现芯片间的直接电连接,同时提供优异的电气性能和热管理能力。

对混合键合呼声最高的非HBM(高带宽存储)芯片莫属。这两年,随着生成式AI技术的迅速崛起,HBM和AI芯片的发展势如破竹。为了迎合市场需求,存储制造商加速了HBM芯片的研发,混合键合一度成为实现下一代HBM(HBM4)中的重要技术。

然而近日行业的风向似乎发生了一些转变,混合键合,是3D封装的未来?还是昙花一现?

下一代HBM弃用混合键合?

在下一代的HBM芯片规划中,两大重量级玩家SK海力士(55%的市占)和三星(41%),此前正在HBM4中积极推进“混合键合”新工艺的开发。

为何要采用混合键合?在此之前,让我们先来了解下HBM的标准发展情况。自2013年10月开始,JEDEC开始发布HBM的标准,至今已经发布了5代HBM标准和产品,分别是HBM、HBM2、HBM2E、HBM3、HBM3E。如下图所示,每一代HBM标准都主要围绕着提供更高的带宽和容量来制定,当然还有更低的功耗等其他功能。

(来源:Rambus)

要实现下一代更高容量和更高带宽的HBM,HBM中的DRAM就需要不断“盖楼”,也就是要堆叠更多的DRAM层。第六代HBM4预计于2026年量产。目前HBM3堆叠了12层,HBM4堆叠的数量可能高达16层,多了4层。随着层数变高,会出现翘曲和发热等因素,但最大的挑战是必须满足当下HBM芯片的标准厚度——720微米(μm)。

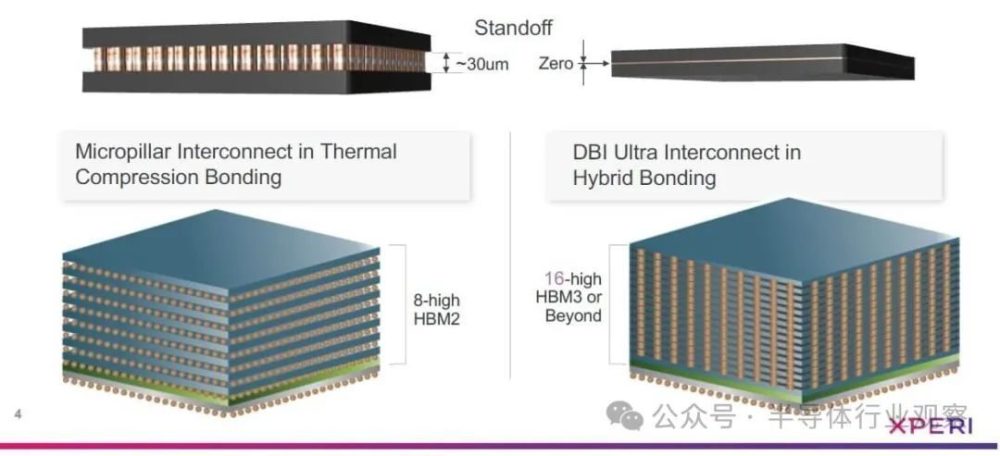

如何解决呢?一种方式是基于现有的互联技术,将每个DRAM层磨薄,但这不能保证其可靠性;另外一种方式是DRAM层与层之间从互联的填充物方面下手,考虑去掉内部的凸块。

现在的HBM内部通过TSV+填充物的方式来连接DRAM层。三星和SK海力士的方法有所差别:三星采用 TC 焊接法,即在 DRAM之间夹上一层不导电的粘合剂薄膜 (NCF),然后进行热压;SK海力士采用MR-MUF(大规模回流注塑填充)技术,对整个 HBM 进行加热和焊接,然后在芯片之间放置液态保护材料以填充缝隙。这些填充物在其中占据了一定的厚度,因此厂商们开始考虑去掉这些填充物,改用混合键合的方式。如前文所述,混合键合可以直接实现芯片和晶圆之间的互联,由于不使用凸块,因此有利于减小封装厚度。

混合键合的概念图。展示了如何通过去除现有键合中芯片之间的凸块来减少整体封装厚度(左)(来源:XPERI)

混合键合的优势主要有三大方面:

更短的互联距离:不仅不需要用引线互联互通,也无需用TSV穿过整个CMOS层,仅仅通过连接后道的铜触点就可以实现互联;

更高的互联密度:铜触点的面积非常小,相比直径百微米的锡球和TSV,混合键合工艺中的铜触点的pitch size甚至都不足10微米,无疑可以实现更高的互联密度;

更低的成本:毫无疑问,针对每颗Die单独进行互联需要更多的时间,通过晶圆键合可以实现大面积高密度的互联,对产能的提升的贡献是飞跃性的!自然,生产成本也可以得以降低。

SK海力士和三星都对混合键合技术进行了不少研究。例如,SK海力士在IEDM 2023上,就透露了其已确保HBM制造中使用的混合键合工艺的可靠性。从公开信息来看,SK海力士预计将在2025至2026年间实现其混合键合技术的商业化。

就在大家以为混合键合将成为HBM4的基本技术时,一则消息可能会改变这个发展趋势。据zdnet报道,制定HBM4标准的标准化组织JEDEC目前正在商榷打算放宽HBM4的封装厚度,由720微米放宽到775微米。如果是按照这个厚度标准,有业内消息称,利用现有的键合技术就可以充分实现16层HBM4。

据悉,制定标准的实体包括存储器供应商以及无晶圆厂公司,它们是 HBM 的实际客户。据称,三星电子、SK海力士、美光三大内存公司从供应商的角度坚持775微米。但由于部分参会企业表达了不同意见,第一轮磋商最终没有得出明确结论。目前,业界正在等待第二次咨询。

不过,围绕HBM4的封装生态系统的方向很可能将根据该协议的方向来确定。

混合键合的商用不是易事。相比传统互联技术,混合键合的工艺流程更加复杂,增加了一些未使用过的技术,如混合键合工艺涉及在真空室中将等离子体辐射到 DRAM 芯片以激活接合处的表面。这是现有封装工艺中尚未使用的技术。而且,混合键合技术尚处于起步阶段,产业链配套能力不足,相关设备和材料的成本较高,最终导致混合键合技术很昂贵。

因此,在满足所有客户要求的情况下,内存制造商希望尽可能避免在 HBM4 中引入混合键合。

这家混合键合设备公司遭殃了

而这则新闻,对于早期投入混合键合设备的供应商Besi产生了重大的影响。从3月7日到3月12日,Besi的股价一路下跌,跌去了大约23%。成立于1995年5月的BE Semiconductor Industries NV(Besi),是一家荷兰半导体设备公司。这家荷兰设备制造商因为所生产的混合键合设备,搭上了AI顺风车,获得了市场和投资者的关注。整个2023年,Besi的股价大涨了141%(从2022年的56.56欧元,到2023年末的136.45欧元),使Besi成为欧洲科技行业估值最高的公司之一。

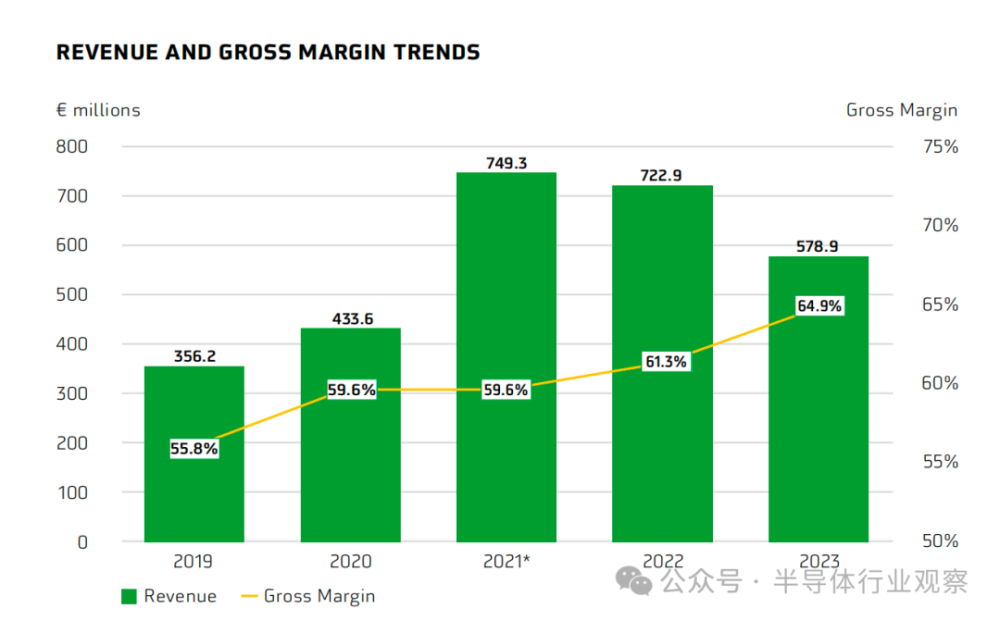

台积电是Besi的老客户,两家公司在键合机领域已经合作了8年多。2021年,在新冠危机期间的半导体热潮中,Besi宣布英特尔和台积电均承诺采购50台混合键合机。也是在这之后的2年里,Besi的营收大幅上涨,2021年期营收达到7.49亿欧元,同比大增73%。

Besi过去5年的收入和毛利率趋势

(来源:Besi财报)

2023年受到市场不景气的影响,其营收有所下滑,但是其财报指出,该公司在光子学、混合键合和 2.5D 逻辑/内存应用领域实现强劲增长。2023年与上一年相比,该公司的订单量大约增加了一倍。其中比较亮眼的是,Besi第四季度1.66 亿欧元的订单中约有一半是新型混合键合机。

Besi还在其2023年财报中指出,混合键合技术的采用日益增加,具体表现在:设备安装基数增至40台设备并且在多条生产线上安装了几套系统。客户数量增加。与2022年相比,订单量和年终库存量翻倍。收到HBM产品的首批订单。为晶圆首次交付了TCB芯片。为2.5D HBM/逻辑设备首次运送翻转芯片系统。

Besi还与应用材料在混合键合领域也有着密切的合作。2020年10月,Besi和应用材料公司签署了一份联合开发协议,两家在新加坡建立了一个中心来开发业界首个集成的基于晶片的混合键合设备解决方案。完整的基于芯片的混合键合设备解决方案需要广泛的半导体制造技术以及高速和极其精确的小芯片贴装技术。应用材料在刻蚀、化学气相沉积(CVD)、物理气相沉积(PVD)、铜电镀、化学机械平坦化(CMP)和过程控制中的知识可以帮助到Besi来开发混合键合新设备。

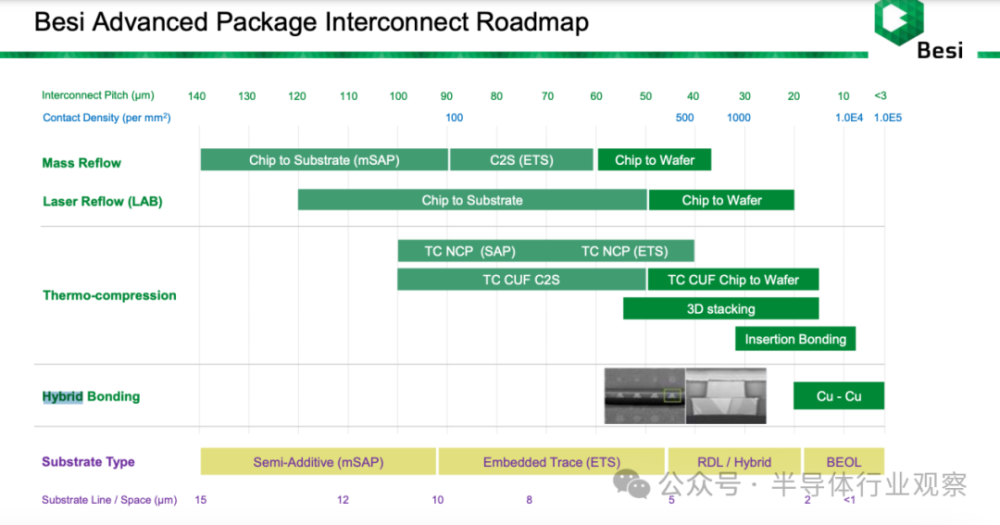

Besi公司高级封装互连技术的路线图

Datacon 8800 CHAMEO ultra plus是Besi的芯片到晶圆键合机。这是第一台大批量芯片到晶圆混合键合机,自2022年开始生产。2023年,Besi正在开发下一代100纳米精度的混合键合系统。

Datacon 8800 CHAMEO

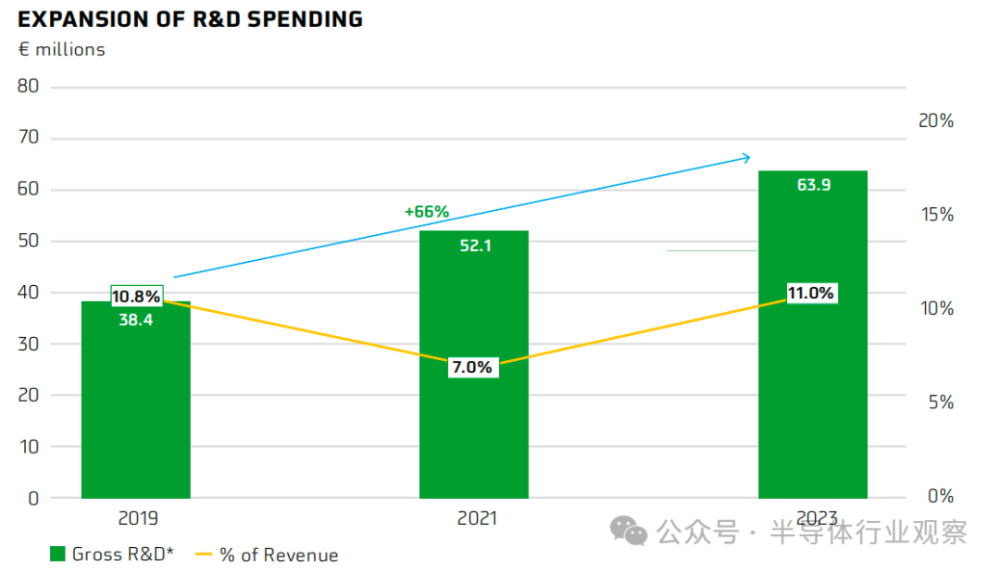

股市的波动反映了其脆弱性。如果HBM4标准确实放宽了厚度,那么市场对Besi及其混合键合设备的需求可能会大幅下降或延期采购(可能要到2026年之后才会采用该技术)。Besi在混合键合技术研发方面投入了大量资金,2023年,Besi总研发支出达到6390万欧元,占总收入的11.0%,与2019年相比增长了66%。如果该技术无法得到广泛应用,这些研发投入将可能成为沉没成本。

Besi最近3年研发支出情况

混合键合,仍然是大势所趋!

尽管面临着诸多挑战,混合键合技术仍是未来芯片互联技术的发展方向之一。目前,混合键合已经成功用于商业生产数据中心和其他高性能计算应用的高端逻辑设备。

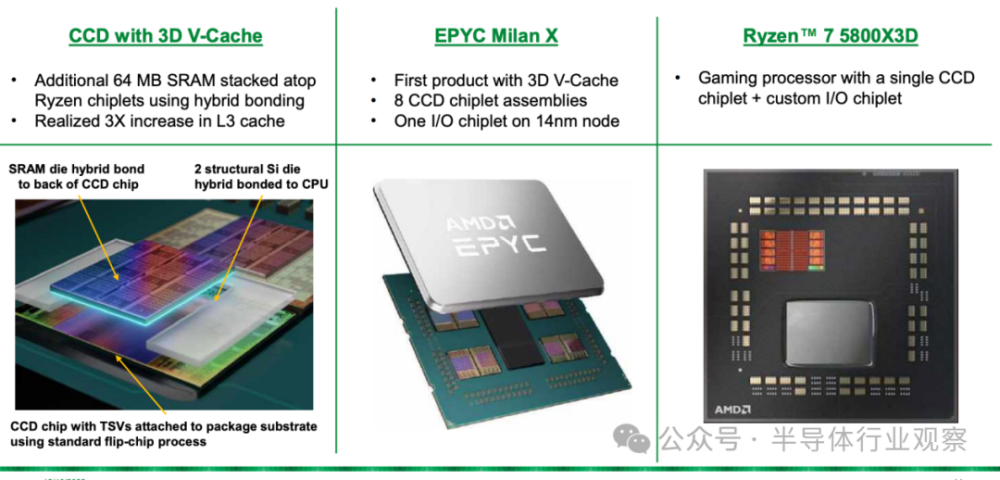

AMD 是第一家推出采用铜混合键合芯片的供应商。在AMD Ryzen 7 5800x的小芯片设计中,就采用了台积电的混合键合技术SoIC,将7nm 64MB SRAM堆叠并键合到 7nm 处理器上,使内存密度增加了两倍。

来源:Besi

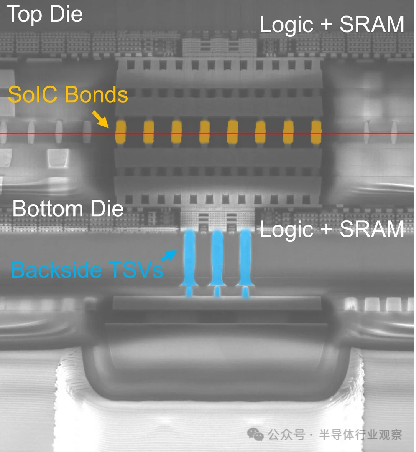

Meta在2024 IEEE 国际固态电路会议 (ISSCC)介绍了其最新的AR处理器,这是一个3D堆叠芯片,其中就使用了混合键合工艺。原型芯片是两个尺寸相同的 IC:4.1 x 3.7 毫米,每个硅片上都具有逻辑和存储器,它们面对面晶圆对晶圆混合键合的工艺键合在一起。据其称,该3D芯片可以同时跟踪两只手,功耗比单个芯片仅跟踪一只手的功耗少 40%。更重要的是,速度提高了40%。

Meta的AR处理器原型芯片

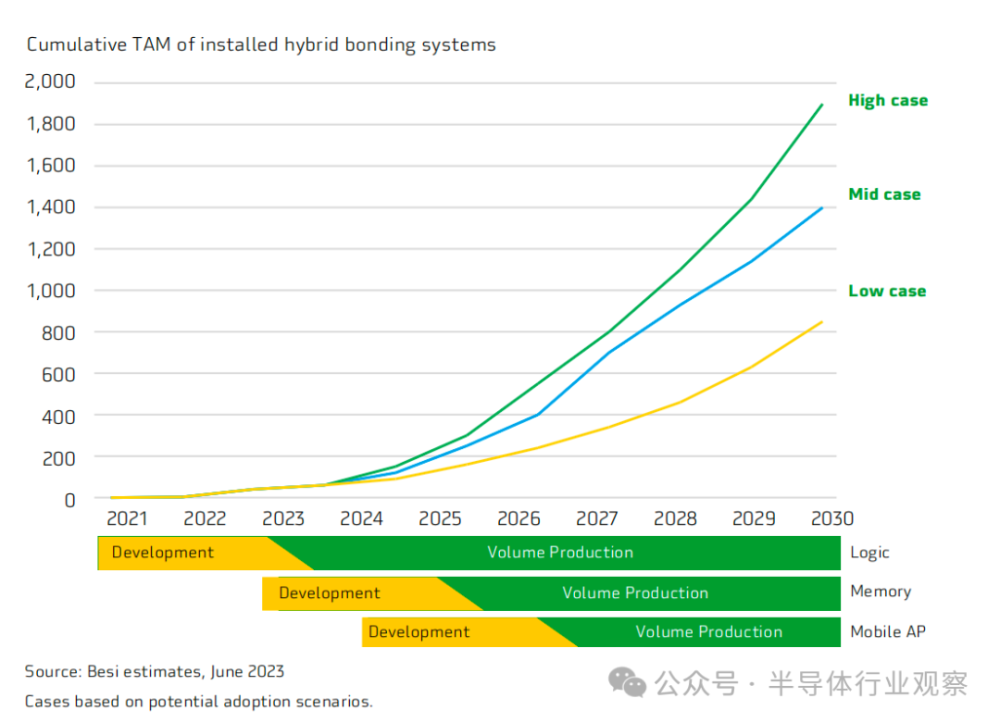

混合键合的潜在应用还有很多,Yole指出,芯片到晶圆混合键合技术即将渗透到服务器、数据中心以及未来的移动应用处理器(APUs)系统中。Besi也表示,混合键合有潜力在未来十年成为3纳米以下器件的领先组装解决方案。预计存储领域未来贡献混合键合设备明显增量,保守预计2026年需求量超过200台。

混合键合的潜在市场应用

(来源:Besi)

目前,全球最大的晶圆厂商们正在评估其在未来封装路线图中的采用。台积电、英特尔和三星都是混合键合技术的拥护者。具体来看,台积电是迄今为止唯一一家将混合键合商业化的芯片公司。三星已经在天安园区封装生产基地建设混合键合产线,预计将用于 X-Cube 和 SAINT 等下一代封装解决方案。英特尔计划将这一技术应用于其3D封装技术Foveros Direct,其中值得一提的是,英特尔正在发展背面供电(PowerVia)技术,其中晶圆间键合是关键步骤。

Besi预估,混合键合市场的规模处于其预估市场大小的中点。预计最大的半导体生产商将在未来五年内采用此技术,之后OSAT厂商也会进一步采用。混合键合设备的平均售价将显著高于目前最先进的Flip chip(倒装芯片)或TCB键合系统。据Besi估计,每台键合设备的成本在200万至250万欧元之间。

从国内情况来看,多家设备制造商正积极进入混合键合领域。据了解,拓荆科技的晶圆对晶圆键合产品(Dione300)已实现产业化应用,芯片对晶圆键合表面预处理产品(Pollux)已出货至客户端验证。芯源微的临时键合机、解键合机已实现国内多家客户订单导入。华卓清科的UP HBS300晶圆级键合机对标的是国际厂商EVG。另外,去年12月完成新一轮超亿元融资的国产设备厂商芯睿科技,主攻半导体晶圆键合设备,目前wafer to wafer的混合键合研发已经在进行当中。国内厂商在混合键合领域的快速发展,将为我国半导体产业的升级提供有力支撑。

总体来看,晶圆间混合键合已成为一种很有前景的3D集成技术,可实现不断增加的 I/O 密度以及功能芯片之间更高效的连接。随着技术的不断进步和产业链的完善,混合键合技术有望在更多领域得到应用,国内设备厂商也将迎来更大的发展机遇。

结论:尽管混合键合这一新型互联技术看起来充满了机会,但其普及性和市场接受度仍存在疑问。不过,混合键合将继续作为未来的趋势,并可能在更小的尺寸下得到广泛应用。然而,由于其复杂的生产工艺和技术成本较高,许多设备制造商可能无法承担其在高带宽存储和尖端内存市场上的需求。

建议:存储制造商应继续投资混合键合工艺的研究和发展,以满足未来需求。此外,政策调整也可能是影响混合键合发展的关键因素。政府应鼓励提供额外的资金支持和优惠条件,以促进这种新兴技术的发展和应用。同时,生产线优化和成本控制也是关键,以提高混合键合的竞争力。